1 Answer1. module pri16to4 (input wire [15:0] in, output wire valid, output wire [3:0] out); wire [1:0] pe3, pe2, pe1, pe0; U3 (in [15:12], pe3); U2 (in [11:8], pe2); U1 (in [7:4], pe1); U0 (in [3:0], pe0); assign valid = (in != 0); assign out = (in [15:12] != 0)? {2'b11, pe3} : (in [11:8] != 0)? {2'b10, pe2} : (in [7:4] != 0) Hence, the Verilog code for the priority encoder in structural style is: module or_gate(c,a,b); input a,b; output c; assign c = a|b; endmodule module not_gate(f,e); input e; output f; assign f = ~e; endmodule module and_gate(z,x,y); input x,y; output z; assign z = x&y; endmodule module priority_encoder_struct(A0,A1,Y0,Y1,Y2,Y3) Verilog Code for 8-Bit ALU; Design 8x3 Priority Encoder in Verilog Coding and Verilog Code for 4x16 Decoder; Verilog Code for D-Latch; Verilog Code for 4-Bit Full Adder using 1-Bit Adder; Verilog Code for 1-bit Adder; VHDL Code for Round Robin Arbiter with Fixed Time VHDL Code for Fixed Priority Arbiter; VHDL Code for Synchronous FIF

- 4 To 16 Decoder Using 2 To 4 Decoder Verilog Codes

- 4 To 16 Decoder Using 2 To 4 Decoder With Enable

- 4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Using

- 4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Examples

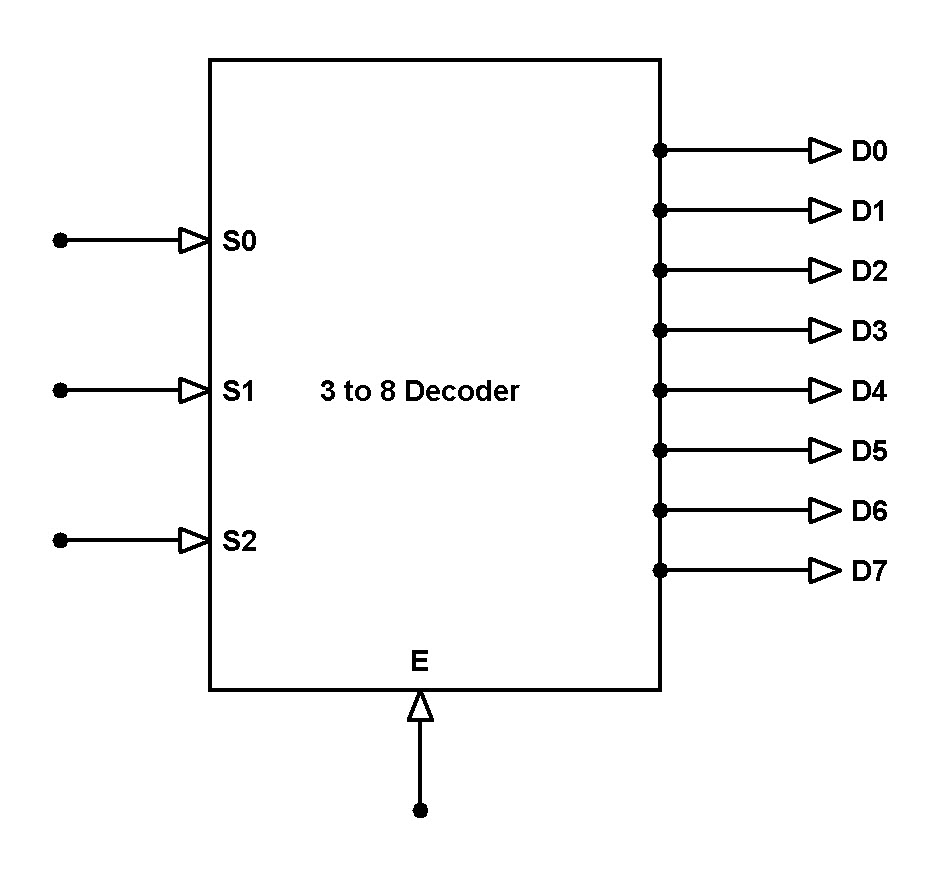

2: 4 Decoder Design using Logical Gates (Data Flow Modeling Style). Output Waveform: 2 to 4 Decoder Verilog CODE- //-. Monday, 15 July 2013. Designing of 2 to 4 Line Decoder Circuit. Similar to the multiplexer circuit, the decoder is not restricted to a particular address line, and thus can have more than two outputs (with two, three, or four address lines). The decoder circuit can decode a 2, 3, or 4-bit binary number, or can decode up to 4, 8, or 16 time-multiplexed signals.

Decoder Design Using Predecoding.Example: 256-output (8 input bits) with predecode –Ex: take groups of 2 input bits.Four possibilities; activate one of four wires (use 2 INVs, 4 ANDs) –Wires along array: 22. (8/2) = 4 groups of 4 = 16 (same as non-predecoded) –Each output uses a 4. Objective: To design 2 to 4 line decoder using Verilog HDL, obtain the simulation and synthesis. Software and Hardware: Xilinx ISE 9.2i and FPGA Spartan-3E. Theory: Decoders are circuits with two or more inputs and 2 n outputs. Based on the input code, only one of the output is selected. The truth table of 2-to-4 line decoder is.

Verilog code for ENCODER using CASE module encoder_using_case(binary_out, // 4 bit binary Output encoder_in, // 16-bit Input enable // Enable for the enco view the full answe Write A Verilog code to built a 16x4 Encoder with priority for lowest weight use always in your implementation. COMPANY About Cheg verilog code for ENCODER using CASE. module encoder_using_case ( 8 binary_out , // 4 bit binary Output 9 encoder_in , // 16-bit Input 10 enable // Enable for the encoder 11 ); 12 output [3:0] binary_out ; 13 input enable ; 14 input [15:0] encoder_in ; 15 16 reg [3:0] binary_out ; 17 18 always @ (enable or encoder_in) 19 begin 20 binary_out = 0; 21. Hi, I want to write verilog-a code for a 4x16 decoder. Can any one help me with this issue. Thanks in advance For each case the decoder should output a 16-bit digit with only one of the bits high. I can't manage to get all the desired outputs when I run the program. Here is the code for the Decoder and test, and the output at the console: 4x16 Decoder: module Decoder4x16 (input [3:0] select, input enable, output reg [16:0] out); always @ (select, enable).

verilog - creating 16to4 bit priority encoder with 4to2

- g Series - 2 to 4 Decoder November 7, 2019 May 16, 2020 Sivakumar P R This video explains how to write a synthesizable Verilog program for 2to4 Decoder using the 'case' statement and the importance of default statement while implementing the combinational logic

- begin. if (en0) dec=7'b00000000; else if (en1) case (i) 0 : dec=7'b00000001; 1 : dec=7'b00000010; 2 : dec=7'b00000100; 3 : dec=7'b00001000; 4 : dec=7'b00010000

- 1 //----- 2 // Design Name : encoder_using_if 3 // File Name : encoder_using_if.v 4 // Function : Encoder using If 5 // Coder : Deepak Kumar Tala 6 //----- 7 module encoder_using_if( 8 binary_out , // 4 bit binary output 9 encoder_in , // 16-bit input 10 enable // Enable for the encoder 11); 12 //-----Output Ports----- 13 output [3:0] binary_out ; 14 //-----Input Ports----- 15 input enable ; 16 input [15:0] encoder_in ; 17 //-----Internal Variables----- 18 reg [3:0] binary_out ; 19.

- I'm afraid that depends on how you combine the 16 and the 4 a detail that you haven't described in the question. Here are a few possibilities. Most of them are not fractions. -- 16 + 4 = 20 -- 16 - 4 = 12 -- 16/4 = 4 -- 4/16 = 1/4 -- 4 - 16 = -12 -- 16 * 4 = 64 -- 164 = 65,536 -- 416 = 4,294,967,29

- input d0,d1,d2,d3,d4,d5,d6,d7; output a,b,c; or (a,d4,d5,d6,d7); or (b,d2,d3,d6,d7); or (c,d1,d3,d5,d7); endmodule. Testbench Code for 8:3 Encoder. `timescale 1ns / 1ps. ///////////////////////////////////////////////////////////////////////////

VHDL Code for 2 to 4 decoder; VHDL Code for 4 to 2 Encoder; About Us.Generic 2's complement Adder/Subtractor Unit . 4-to-16 Decoder (XDC included): . (VHDL main file) Generic Serial Multiplier (NxN, unsigned .I've a design problem in VHDL with a serial adder. Verilog code for ALU (16 Operations ) DESIGN AND IMPLEMENTATION OF ALU USING FPGA SPARTAN 2; REGISTERS. One thought on verilog code for encoder and testbench Preetha says: March 2, 2014 at 1:18 pm. Plz uplod files fr 2:4 encoder..and decoder. Reply. Leave a Reply Cancel reply 4 : 2 Encoder using Logical Gates (Verilog CODE). 2 : 4 Decoder using Logical Gates (Verilog CODE). Half Subtractor Design using Logical Expression (V... 1 : 4 Demultiplexer Design using Gates (Verilog CO... 4 to 1 Multiplexer Design using Logical Expression... Full Subtractor Design using Logical Gates (Verilo..

Verilog code for priority encoder - All modeling style

- al ports

- Verilog source codes Low Pass FIR Filter Asynchronous FIFO D FF without reset D FF synchronous reset 1 bit 4 bit comparator Binary counter BCD Gray counter T,D,SR,JK FF 32 bit ALU Full Adder 4 to 1 MUX DEMUX binary2Gray converter 8to1 MUX 8to3 Encoder Logic Gates Half adder substractor 2to4 decode

- It can be 4-to-2, 8-to-3 and 16-to-4 line configurations. VHDL Code for 4 to 2 encoder can be designed both in structural and behavioral modelling. 4 to 2 encoder design using logic gate

- 1 //----- 2 // Design Name : encoder_using_case 3 // File Name : encoder_using_case.sv 4 // Function : Encoder using Case 5 // Coder : Deepak Kumar Tala 6 //----- 7 module encoder_using_case( 8 output reg [3:0] binary_out , // 4 bit binary Output 9 input wire [15:0] encoder_in , // 16-bit Input 10 input wire enable // Enable for the encoder 11); 12 //-----Code Starts Here----- 13 always_comb.

- Verilog VHDL code Decoder and Encoder. 1. Experiment 4 Name: SHYAMVEER SINGH Roll no. B-54 Regno. 11205816 AIM: To implement the 2:4,3:8, Decode and 8:3 encoder using dataflow modeling and bheverioural madeling. Apparetus: Xillinx ISE 9.2i softwere Implementation of 2:4 Decoder: Enable a b y0 y1 y2 y3 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1.

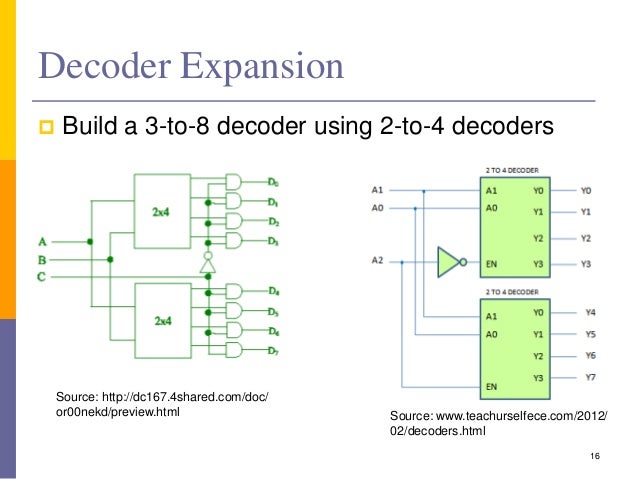

- A decoder circuit of the higher combination is obtained by adding two or more lower combinational circuits. 4 to 16 decoder circuit is obtained from two 3 to 8 decoder circuits or three 2 to 4 decoder circuits. When two 3 to 8 Decoder circuits are combined the enable pin acts as the input for both the decoders

- In this lecture, we are implementing 2:4 Decoder using verilog HDL.Channel Playlist (ALL): https://www.youtube.com/... This lecture is part of Verilog Tutorial

Verilog Code for 1 to 4 DEMUX Structural/Gate Level Modelling 1-4 DEMUX module demux_1_to_4( input d, input s0, input s1, output y0, output y1, output y2, output y3 ); not(s1n,s1),(s0n,s0); and(y0,d,s0n,s1n),(y1,d,s0,s1n),(y2,d,s0n,s1),(y3,d,s0,s1); endmodule //Testbench code for 1 to 4 DEMUX Structural/Gate Level Modelling initial begin // Initialize Inputs d = 1; s0 = 0; s1 = 0; // Wait 100. Objective: To design 2 to 4 line decoder using Verilog HDL, obtain the simulation and synthesis. Software and Hardware: Xilinx ISE 9.2i and FPGA Spartan-3E. Theory

VLSICoding: Verilog Code for 4x16 Decode

- In this post, we will write the VHDL code for a 4:2 encoder using its logic equations and its truth table. Logic circuit of a 4:2 encoder A 4:2 encoder has four input ports and two output ports

- Verilog code for Radix 4 Booth's Multiplication. Contribute to ym97/radix4 development by creating an account on GitHub

- In this Verilog project, Verilog code for decoder is presented. The decoder is used for memory address decoding. The decoder as shown in the figure above decodes the 5-bit address input and outputs a 32-bit signal to select the address being written in the memory

- -Total of 8 + 8 + 4 = 20 predecoded wires •Example: predecode groups of 4 address bits -Predecoding groups: 4 + 4 for the same 8:256 decoder -Each predecode group has 2^4 = 16 output wires -Each predecoded wire has N/16 loads -Total of 16 + 16 = 32 predecoded wire

- Tags: 4 to 16 decoder Verilog code, decoder verilog code, verilog project. 0. Decoder is a digital circuit that can select a line according to the input pattern. Decoder can be used as a control unit for a MCU,processor etc. 4 to 16 line decoder verilog code arr given bellow

- Verilog File Operations Code Examples Hello World! Flops and Latches JK Flip-Flop D Flip-Flop T Flip-Flop D Latch Counters 4-bit counter Ripple Counter Straight Ring Counter Johnson Counter Mod-N Counter Gray Counter Misc n-bit Shift Register Priority Encoder 4x1 multiplexer Full adder Single Port RAM.

- Encoder (VHDL and Verilog) 16 Choose VHDL Test Bench and select a name for the Test Bench (TB). NOTE: As you would expect, an equivalent Verilog Design will result in exactly the same logic being produced and the same simulation results. Start Project Navigator

Solved: Write A Verilog Module For A 16-4 Priority Encoder

- g language.The fig-1 depicts 2 to 4 decoder schematic symbol and following is the truth table for.Thus, each output of the decoder will be generated to the input combination.Regularly we gó over applications whére it is éxpected to nourish á few input signaIs to a soIitary load, each át once

- website builder. Create your website today. Start Now. A verilog portal for needs. eriloGcod

- I'm looking for a chip that has 16 inputs where if only one of the inputs go high then it encodes the data to a 4 bit output. If one doesn't exist what would be the simplest way to build such a cir..

- Monday, November 16, 2015. Verilog code for 4 bit Wallace tree multiplier Few years back I wrote the VHDL code for a 4 bit Wallace tree multiplier. In this post I want to convert the VHDL into a Verilog code. A Wallace tree multiplier is much faster than the normal multiplier designs

- 4 bit Binary to Gray code and Gray code to Binary converter in Verilog UPDATE : A GENERIC GRAY CODE CONVERTER IS AVAILABLE HERE Gray codes are non-weighted codes, where two successive values differ only on one bit

- 16 point IFFT,READ MORE. Correlation matlab code with comparison to matlab function, READ MORE. 8 to 3 Encoder, Read More. Verilog codes for All the logic gates, Read More. Half adder, Half substractor, Full substractor codes, Read More. 2 to 4 Decoder code, Read More. Labview Source codes

- A 4 to 2 priority encoder has 4 inputs: Y3, Y2, Y1 & Y0 and 2 outputs: A1 & A0. Here, the input, Y3 has the highest priority , whereas the input, Y0 has the lowest priority . In this case, even if more than one input is '1' at the same time, the output will be the (binary) code corresponding to the input, which is having higher priority

VLSI DESIGN, VERILOG CODE, VHDL CODE Hello everyone; This is my first post. I built a 16 bit, 4 concentric circle Gray Code Wheel, with Infrared emitters and detectors to read the Gray Code to drive 16 small LEDs arranged to indicate every 22.5 degrees of a compass circle. The object of this device is to indicate the direction..

Verilog Code for (7,4) Systematic Hamming Encoder This code will encode four bits of data and generate seven bits of code by adding three bits as parity bits. It was introduced by Richard W. Hamming write a verilog program for 2 to 4 decoder A decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different. The enable inputs must be ON for the decoder to function, otherwise its outputs assumes a 'disabled' output code word The verilog is written in such a way as to be easily parameterized for different values of n and k. If there is any interest for parameterization, let me know and I will create a version 2 core. Otherwise the core as is can be used to implement for example, a (255, 239) or (204, 188) codes

Solved: Write A Verilog Code To Built A 16x4 Encoder With

Figure 7-4 Verilog Coding Format (Page 2) R 7.8.16 Macromodules are not allowed R 7.8.17 Operand sizes must match R 7.8.18 Connect ports by name in module instantiations G 7.8.25 Next-state encoding of state machines should be made through the use of case statement Encoding Radix-4 8-bit Here is the sign extension for 16 bit x 16 bit. Here shift two bit for each partial product, and also we extend 9bit result to 12bit. In order to make sure about the multiplication procedure we wrote the verilog code for all the block

vlsi world: verilog code for ENCODER using CAS

It can be 2-to-4, 3-to-8 and 4-to-16 line configurations. Binary decoder can be easily constructed using basic logic gates. Similar to Encoder Design, VHDL Code for 2 to 4 decoder can be done in different methods like using case statement, using if else statement, using logic gates etc Verilog code for counter,Verilog code for counter with testbench, verilog code for up counter, verilog code for down counter, 16. Verilog code for Alarm Clock on FPGA 17. Verilog code for comparator design 18. Verilog code for D Flip Flop 19. Verilog code for Full Adder 20 Verilog code for ALU (16 Operations ) DESIGN AND IMPLEMENTATION OF ALU USING FPGA SPARTAN 2; REGISTERS. verilog code for 4-bit Shift Register; verilog code for encoder and testbench; verilog code for decoder and testbench; verilog code for 4 bit mux and test bench; COMPARATORS Altera Corporation 1 8b10b Encoder/Decoder MegaCore Function (ED8B10B) November 2001; ver. 1.02 Data Sheet A-DS-IPED8B10B-1.02 Introduction Encoders and decoders are used for physical layer coding for Gigabit Ethernet, Fibre Channel, and other applications Four 4 to 2 encoders are connected to the 16 inputs and the 8 outputs are again connected to the two 4 to 2 encoders , which produces 4 outputs. Priority Encoder applications As compared with the standard digital encoder, a priority encoder is most commonly used in several applications

.. HDL code 4-to-2 Priority Encoder Prerequisites: Study the functionality of Priority Encoder. Learning Objective: To develop the source code for 4 to 2 line priority encoder by using VERILOG and obtain the simulation and synthesis

VERILOG CODES/PROJECTS VERILOG VDHL PROGRAMS NEW PROJECTS ADDED: RS232 Transmitter receiver Hie friends, here are few programs i want to make open source for u guys. These programs are based on hdl and i have used verilog to code the design, [use cntrl+f and type the program name to directly go to the code u need 6) Verilog code to simulate 8:3 priority encoder As already discussed always, In this program sensitivity lists are en, i. Because output depends on this two only, that's why they are sensitive verilog tutorial and programs with testbench code - Random Acess Memory. Home; Programs. Verilog programs. Verilog program for Basic Logic Gates; Verilog program for Half Adder; Verilog program for 8:3 Encoder Verilog program for 1:8 Demultiplxer Verilog program for 8:1 Multiplexer Verilog program for 8bit D Flipflop Verilog program for T. Reed-Solomon codes may be shortened by (conceptually) making a number of data symbols zero at the encoder, not transmitting them, and then re-inserting them at the decoder. Example : The (255,223) code described above can be shortened to (200,168) . If you wish to use commercial simulators, you need a validated account. If you have already registered (or have recently changed your email address), but have not clicked on the link in the email we sent you, please do so

Verilog code for 4 to 2 line Encoder; Verilog code for 1:2 DEMUX; Verilog code for 4:1 MUX; Verilog code for 2:1 MUX; Verilog code for Full-Adder; Verilog code for Half-Adder; Verilog code for XOR gate; Verilog code for XNOR gate; Verilog code for NOT gate; Verilog code for NOR gate Verilog VHDL code Multiplexer and De Multiplexer 1. Experiment 3 Name: Shyamveer Singh Reg no:11205816 Rollno:B-54 AIM: To implement the multiplexer and demultiplexer with data flow and gate level molding

. The operation is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence verilog RTL级代码编写指导(20篇精华文章)目录: Actel HDL Coding Style Guide; Advanced High-level HDL Design Techniques for Programmable Logic; Designing Safe Verilog State Machines with Synplify; fpga优秀设计的十条戒律; Guide to HDL Coding Styles for Synthesis; IEEE P1364.1_IEEE Standard for Verilog Register Transfer Level Synthesis; IEEE P1364.1D1.4. Project 5: Multiplexer, Decoder, Encoder, and Shifter: In this project you will design a multiplexer, a decoder, an encoder, and a shifter using Verilog HDL. Instead of building the circuit using logic operators, you will learn to describe a circuit behaviorally according to the functionality you

. Experiment 4 Name: SHYAMVEER SINGH Roll no. B-54 Regno. 11205816 AIM: To implement the 2:4,3:8, Decode and 8:3 encoder using dataflow modeling and bheverioural madeling DESIGN OF HAMMING CODE USING VERILOG HDL H amming code is an error-correction code that can be used to detect single and is the (11, 7, 1) Hamming code encoder that converts a 7-bit ASCII code into an 11-bit code word and the Ham-ming_ Decode.v is the (11, 7, 1) Ham-ming code decoder that converts an 11-bit code word back into a 7-bi 10 TO 4 LINE PRIORITY ENCODER B1R (Plastic Package) ORDER CODES : M54HC147F1R M74HC147M1R M74HC147B1R M74HC147C1R F1R (CeramicPackage) M1R The M54/74HC147 is ahigh speed CMOS 10 TO 4 LINE PRIORITY ENCODER fabricated in silicon gate C2MOS technology. 16 VCC Positive Supply Voltage IEC LOGIC SYMBOL ABSOLUTE MAXIMUM RATING Verilog Source Code. Jim Duckworth, WPI 11 Verilog Module Rev A Concurrent statements • VHDL WPI 16 Verilog Module Rev A Decoder - always statement Related source file is C:ece3829encoderencoder.v. WARNING:Xst:647 - Input <i0> is never used

[7] FPGA Implementation of Reed-Solomon Encoder and Decoder for Wireless Network 802.16 - International Journal of Computer Applications (0975 - 8887) Volume 68- No.16, April 2013, Priyanka Dayal, Rajeev Kumar Patia Generally, digital encoders produce outputs of 2-bit, 3-bit or 4-bit codes depending upon the number of data input lines. An n-bit binary encoder has 2 n input lines and n-bit output lines with common types that include 4-to-2, 8-to-3 and 16-to-4 line configurations Priority encoders can be easily connected in arrays to make larger encoders, such as one 16-to-4 encoder made from six 4-to-2 priority encoders - four 4-to-2 encoders having the signal source connected to their inputs, and the two remaining encoders take the output of the first four as input

May 2011 Altera Corporation 8B10B Encoder/Decoder MegaCore Function User Guide 1. About This MegaCore Function Release Information Table 1-1 provides information about this release of the Altera ® 8B10B Encoder/Decoder MegaCore® function. f For more information about this release, refer to the MegaCore IP Library Release Notes and Errata 2 : 4 Decoder Design using Logical Gates (Data Flow Modeling Style). Output Waveform : 2 to 4 Decoder Verilog CODE- //------..

4 www.xilinx.com XAPP339 (v1.3) October 1, 2002 1-800-255-7778 R Manchester Encoder-Decoder for Xilinx CPLDs Manchester Encoder/ Decoder Functionality The functions of the encoder section of the MED include a microprocessor interface, parallel t . We saw that the Verilog Casex and Casez statements can simplify the code when there are don't-care values in our truth table

Verilog-a code for 4x16 decoder Forum for Electronic

D) Since the total inputs are 16, the design shall produce 4 bit code and not 2 sets of 3 bit codes. Hence it is essential to design additional circuit that appends 4 th bit appropriately. This 4th bit, MSB, shall be 0 if any of the 1-8 inputs is active and hence 0 shall be appended to Enc-1 output A priority encoder is an encoder circuit that includes the priority function. The operation of the priority encoder is such that if two or more inputs are equal to at the same time, the input having the highest priority will take precedence. Consider the 4:2 Priority encoder below. Input D3 has the highest precedence, i Hello guys , i have recently worked on vedic multipliers and have referred few papers too to implement it. I want to make this project open to everyone so that you can build your own Vedic multipliers and compare the results.Previously i have written about 2x2 bit Vedic multipliers which you can refer back again. We will start by designing a 2x2 multipliers and will develop a 16x16 multipliers Verilog code for a 3-bit 1-of-9 Priority Encoder Verilog code for a logical shifter Verilog code Following is Verilog code for a 4-bit register with a positive-edge clock, asynchronous set and clock enable. module flop (clk, d, ce, pre, q); input clk, ce, pre. Verilog based BCH encoder/decoder. Choosing a value that is DATA_BITS is usually safe. The code currently compiles under Icarus Verilog, Xilinx Isim and BITS= 1,PIPELINE_STAGES=0,REG_RATIO=1 26 slices 485 MHz BITS= 8,PIPELINE_STAGES=2,REG_RATIO=4 75 slices 457 MHz BITS=16,PIPELINE_STAGES=2,REG_RATIO=8 111 slices 393.

Verilog 4x16 Decoder outputs wrong data - Stack Overflo

4 To 16 Decoder Using 2 To 4 Decoder Verilog Codes

VHDL code for the multiplier and its. verilog code for serial multiplier datasheet, . verilog code for 4 bit ripple COUNTER. verilog procedural simulation filters 16-order using the Adder and multiplier 40KHZ 16-bit into . regular verilog code . verilog uart 115200 Refer to HDL progamming using Verilog and Vhdl by botros for booth multiplier logic. or watch this vide d d e e c c _ _ d d i o --- 1 1 0 1 0 0 0 1 1 1 1 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 1 (C) Computer simulation by Verilog HD

Verilog Programming Series - 2 to 4 Decoder - Maven Silico

verilog code 4:2 encoder Search and download verilog code 4:2 encoder open source project / source codes from CodeForge.co 10-to-4 line priority encoder, 74HC/HCT147,74HCT147D 74HCT147D 74HCT147N 74HCT147U 74HC147D 74HC147D 74HC147DB 74HC147DB 74HC147N 74HC147U Created Date 19970828072000 An encoder with one set of pulses would not be useful because it could not indicate the direction of rotation. Using two code tracks with sectors positioned 90 deg out of phase (Figure 2), the two output channels of the quadrature encoder indicate both position and direction of rotation Verilog Gray Counter with What is Verilog, Lexical Tokens, ASIC Design Flow, For example, a balanced 4-bit Gray code has 16 transitions, The name comes from their use with rotary encoders, where many tracks are being sensed by contacts,. Write a verilog program for 2 to 4 decoder A decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different. The enable inputs must be ON for the decoder to function, otherwise its outputs assumes a 'disabled' output code word

Verilog 4x16 decoder (structural) - lertsirikarn

Found 3-bit 1-of-9 priority encoder for signal <code>. Summary: inferred 3 Priority encoder(s). Unit <priority> synthesized. HDL Synthesis Report Macro Statistics # Priority Encoders Verilog Following is the Verilog code for a 3-bit 1-of-9 Priority Encoder The hexadecimal to 7 segment encoder has 4 bit input and 7 output. Depending upon the input number, some of the 7 segments are displayed. Change the above hex to BCD verilog code so that it take negative logic. A segment is on when it gets 0 Find 16 To 4 Line Priority Encoder related suppliers, manufacturers, products and specifications on GlobalSpec - a trusted source of 16 To 4 Line Priority Encoder information Different ways to code Verilog: A Multiplexer example There are different ways to design a circuit in Verilog. In this tutorial I have used seven different ways to implement a 4 to 1 MUX. After synthesizing, five of them gave same RTL level circuit in Xilinx Project navigator. Let us start with a.

Encoders - asic-world

4 To 16 Decoder Using 2 To 4 Decoder With Enable

Laboratory Exercise #7 5 Table 2: 4:2 Binary Encoder Truth Table w 3 w 2 w 1 w 0 y 1 y 0 zero 0 0 0 0 X X 1 0 0 0 1 0 0 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 0. Block diagram for Decade counter: Verilog code for Decade Counter/ MOD-10 Counter: (Behavioural model) module decade_... 4 to 2 Encoder (Structural Modeling) Full Adder Using NAND Gate (Structural Modeling) kumar I am kumar from Andhra pradesh, INDIA. I have completed M.Tech in VLSI. Getting M.tech degree in VLSI is very easy because now a days all colleges are offering this course VHDL Following is the VHDL code. library ieee; use ieee.std_logic_1164.all; entity dec is port (sel: in std_logic_vector (2 downto 0); res: out std_logic_vector (7 downto 0)); end dec; architecture archi of dec is begin res <= 00000001 when sel = 000 else -- unused decoder output XXXXXXXX when sel = 001 else 00000100 when sel = 010 else 00001000 when sel = 011 else 00010000. Using case statement. Note that the signal out is declared as a reg type because it is used in a procedural block like always.. module mux_4to1_case ( input [3:0] a, // 4-bit input called a input [3:0] b, // 4-bit input called b input [3:0] c, // 4-bit input called c input [3:0] d, // 4-bit input called d input [1:0] sel, // input sel used to select between a,b,c,d output reg [3:0] out); // 4.

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code

Print Verilog Code 4 2 Encoder Module Encoder83 Y Input 3 0 Output 1 0 Y Reg 1 0 Y Always Q3761182 Verilog Code For Encoder [od4p79djjv4p]. VERILOG CODE FOR 8:3ENCODER module encoder1(x,y,z, d); output x,y,z; input [7:0] d; or(x,d[4],d[5],d[6],d[7]),(y,d[2],d[3. In addition to the regular case statements, verilog provides two variations casez and casex. Before we try to understand casex and casez, we need to understand that there are 4 types of logic levels and in verilog

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Using

Verilog code for 8 to 3 Encoder - TECHMASTERPLUS

VerilogCode for 1 to 4 DEMUX Structural/Gate Level Modelling 1-4 DEMUX module demux_1_to_4( input d, input s0, input s1, output y0, output y1, output y2, output y3 ); not(s1n,s1),(s0n,s0); and(y0,d,s0n,s1n),(y1,d,s0,s1n),(y2,d,s0n,s1),(y3,d,s0,s1); endmodule //Testbench code for 1 to 4 DEMUX Structural/Gate Level Modelling initial begin // Initialize Inputs d = 1; s0 = 0; s1 = 0; // Wait 100. Hello! I am brand new to working with Arduino and I have no programming experience, so I am at a loss as to how to read the position of a Grayhill 4-bit, 16 position absolute encoder. Here is the datasheet for that particular encoder (my model is the 25LB22-G). It outputs in Gray code, supposedly. Right now, I just want to be able to serial print its absolute position in a way that's easy to. January 30, 2012 ECE 152A - Digital Design Principles 3 Reading Assignment Brown and Vranesic (cont) 1st edition only! 4Optimized Implementation of Logic Functions 4.12 CAD Tools 4.12.1 Logic Synthesis and Optimization 4.12.2 Physical Design 4.12.3 Timing Simulation 4.12.4 Summary of Design Flow 4.12.5 Examples of Circuits Synthesized from Verilog Code View Prelab 7 from ECEN 248 at Texas A&M University. Lab 7: Introduction to Behavioral Verilog and Logic Synthesis Date: October 16, 2013 1. Verilog code with comments for the 2:4 binary decoder, th

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code - fasrsea; 4 To 16 Decoder Using 2 To 4 Decoder Verilog Code - fasrsea One Hot to Binary Encoder This function will take a one hot binary vector and encode it into binary. If the left most bit of the one hot input is set, the output is zero 4: 25 (encoder_in 16'bxxxx_xxxx_xx10_0000 Verilog Interview Questions Part #4; Verilog Interview Questions Part #3; Verilog Interview About Me. Roy Chan Specialties in ASIC Design and Verification from front-end to back-end activities, including RTL coding, verification (testbench development, testcase generation and test. The dataflow description of a 2-to-4 line decoder is shown in HDL below. Write Verilog HDL dataflow description of a quadruple 2-to-1 line multiplexer with enable. Attach source codes (HDL and stimulus module), waveforms, and implementation report generated b module priority_encoder(I,en_pren,code); input [7:0]I; input en_pren; output reg[2:0]code; always@(*) begin casex(I) Find some verilog beginner codes here.. Menu. Home; About; Home Priority Encoder. Priority Encoder. August 16, 2014 August 16, 2014 VB code. module priority_encoder(I,en_pren,code); input [7:0]I; input en_pren.